# Correct Translation between Weak Memory Model Architectures

Dennis Sprokholt

# Correct Translation between Weak Memory Model Architectures

# Dissertation

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus, prof. dr. ir. T.H.J.J. van der Hagen;

Chair of the Board for Doctorates

to be defended publicly on

Friday 12 December 2025 at 10:00 o'clock

by

# Dennis Guido SPROKHOLT

Master of Science in Computer Science, Utrecht University, the Netherlands This dissertation has been approved by the promotors.

#### Composition of the doctoral committee:

Rector Magnificus chairperson

Prof.dr. K.G. Langendoen Delft University of Technology, *promotor*Dr. S.S. Chakraborty Delft University of Technology, *copromotor*

# **Independent members:**

Prof.dr.ir. G.N. Gaydadjiev Delft University of Technology Prof.dr. P.A. Abdulla Uppsala University, Sweden

Prof.dr. B. Dongol University of Surrey, United Kingdom

Prof.dr. S.B. Scholz Radboud University

Prof.dr. M. Huisman University of Twente

Prof.dr. M.M. de Weerdt Delft University of Technology, reserve member

Prof.dr. Eelco Visser (Delft University of Technology) was the original promotor of this research until his untimely passing on April 5th, 2022.

The work in this dissertation has been carried out at the Delft University of Technology, under the auspices of the research school IPA (Institute for Programming research and Algorithmics).

Copyright © 2025 Dennis Sprokholt – https://dennis.life

Cover image: Copyright © 2025 Dennis Sprokholt Printed by: Gildeprint – https://gildeprint.nl

IPA Dissertation Series: 2025-16

ISBN 978-94-6518-172-1

An electronic version of this dissertation is available at https://repository.tudelft.nl

# Acknowledgements

Thank you to my supervisor, Soham, for your guidance, encouragement, and technical expertise, which were essential to produce the contents of this dissertation. You taught me that finding collaborators to help solve research problems is equally important to finding the problems themselves; this led to many collaborations with diverse perspectives on interesting problems. Thank you to my promotor, Koen, for your practical perspective, insightful questions, and for encouraging me to look at the bigger picture to shape the coherent narrative of this dissertation. Your guarding of the process—particularly by insisting on deadlines—also helped finish it *on time*. Thank you to my late promotor, Eelco, for founding the Programming Languages group and for believing in me enough to offer me a PhD position in it.

Thank you to my collaborators Rodrigo, Redha, Pramod, Tom, Martin, Sebastian, Theo, Krishna, Anish, and Yifan. Our frequent discussions and differing points of view were essential for iterating on the ideas that led to our co-authored papers. Thank you to my committee members, Parosh Aziz Abdulla, Brijesh Dongol, Sven-Bodo Scholz, Marieke Huisman, and Georgi Gaydadjiev, for your time, effort, and valuable feedback on this dissertation. Thank you to the countless anonymous conference reviewers for providing feedback on the included papers.

Thank you to the members of the Delft Programming Languages group for the regular coffee breaks, where we could share our suffering. Thank you (in random order) Luka for "singing" together, Xulei for the plants, Cas for sitting in the hallway eggs, Lucas for the monitor box, Kobe for the whiteboard scribbles, Bohdan for "buying my car", Jaro for the pure FP chats, and Max for being in my gym; thank you Jeff, Andreea, Aron, Danny, Jasper, Casper, Peter, Alex, Elmer, Jesper, Gabriël, Arjen, Sára, and Daniel. Thank you to the interns: Arthur for taking my pictures, Thomas for teaching me to climb, Ewen, Micol, and Houda. Thank you to the support staff Roniet, Shelly, Sophie, Myrthe, and Marja. Thank you to my students, Pieter, Kuba, and Einar; working with you helped me recognize the boundaries of my own understanding — both technical and non-technical. Thank you to all the other people I have enjoyed spending time with while visiting conferences and summer schools.

Thank you to the people who made these PhD years more enjoyable outside university walls. Thank you for the Brouwhuis visits and beach rituals, Máté, Jeffrey, and David. Thank you, Kevin and Joris, for playing Among Us—especially during lockdown. Thank you, Qiao and Labrinus, for the boat trip. Thank you, Thomas, Cas, Max, Kobe, Luka, Jaro, and David, for climbing (and falling) with me.

Thank you to my father and mother, for always supporting and believing in me. Thank you to my sister Laura, and Pieter. Finally, thank you to my girlfriend Dān (尹) for your encouragement, support, and patience throughout this journey.

# **English Summary**

This dissertation is about translating concurrent programs between computer architectures. Legacy programs—built-for and tested-on x86—behave differently on newer architectures, such as Arm and RISC-V. Particularly, weak memory behaviors emerge when two micro-architectural features interact: (i) concurrency, where multiple CPU cores simultaneously execute parts of a program, and (ii) out-of-order execution, where a CPU core reorders instructions to increase throughput. Programs can non-deterministically show one of various weak memory behaviors, meaning it could behave differently when executing again. Those behaviors differ between architectures. When migrating programs from x86 to Arm or RISC-V, the same program could non-deterministically show behaviors never observed on x86.

In part I, we look at *binary translators*, which are software systems that translate compiled binary programs between architectures. We study the translation process of three such real-world systems, identify errors in their translation of concurrency primitives, and fix them. We propose mathematically-rigorous weak memory models for these translators. We then define mapping schemes to translate concurrency primitives one-by-one from x86 to Arm and RISC-V. With the formal semantics, we prove those mapping schemes correct in the Agda proof assistant.

In part II, we study the common structure of our weak memory proofs written in Agda. As those proofs are often large, complex, and rigid, we identify their common structures for which we identify domain-specific abstractions. We implement those abstractions in our novel Agda proof framework Burrow to greatly simplify writing future weak memory proofs.

In part III, we use *dynamic analysis* to identify weak behaviors that were never seen on x86 but could appear on Arm. Our analysis *simulates* the program's execution with the formal weak memory semantics of x86 and Arm. This analysis identifies only the new behaviors the program shows in practice. After finding any new behavior on Arm, we judiciously modify the program to eliminate only that behavior.

# Nederlandse Samenvatting

Deze dissertatie betreft het vertalen van gelijktijdige programma's tussen verschillende computerarchitecturen. Computerprogramma's die zijn geschreven voor en getest op x86 gedragen zich anders op nieuwe architecturen, zoals Arm en RISC-V. Vooral weak memory gedrag verschilt, wat zichtbaar is wanneer twee eigenschappen van microarchitecturen samen komen: (i) gelijktijdigheid, waar meerdere processesoren tegelijkertijd delen van hetzelfde programma uitvoeren, en (ii) out-of-order programma-uitvoering, waar de processor instructies in een andere volgorde uitvoert dan zoals ze in het programma staan. Een programma kan willekeurig één van meerdere weak memory gedragingen laten zien, wat betekent dat het programma zich anders kan gedragen wanneer het opnieuw wordt uitgevoerd. Daarnaast verschilt het mogelijke weak memory gedrag per architectuur. Wanneer een programma wordt vertaald van x86 naar Arm of RISC-V, kan het nieuw gedrag laten zien, dat nooit eerder was waargenomen op x86.

Deel I gaat over *binaire vertalers* die binaire programma's vertalen tussen computerachitecturen. We bestuderen het vertaalproces van drie bestaande vertaalsystemen, waarin we fouten identificeren en repareren in de vertaling van gelijktijdigheidsinstructies. We introduceren rigoreuze wiskundige *weak memory* modellen voor die vertalers. Daarna definiëren we vertaalschema's om gelijktijdigheidsinstructies één voor één te vertalen van x86 naar Arm en RISC-V. Met de formele modellen bewijzen we die vertaalschema's correct in de Agda bewijsassistent.

In deel II bestuderen we de structuur van *weak memory* bewijzen in Agda. Die bewijzen zijn vaak groot, complex, en moeilijk aan te passen. Om die complexiteit te verlagen definiëren we domeinspecifieke abstracties voor hun gemeenschappelijke bewijsstructuur. We implementeren die abstracties in onze Agda bibliotheek Burrow waarmee *weak memory* transformaties makkelijker zijn te bewijzen.

In deel III gebruiken we *dynamische analyse* om *weak memory* gedrag te identificeren dat niet op x86 zichtbaar is maar wel op Arm. Onze analyse simuleert de uitvoering van het programma volgens de formele semantiek van x86 en Arm. Na het vinden van een nieuw gedrag op Arm passen we het programma aan om dat gedrag uit te sluiten. Onze analyse identificeert enkel de gedragingen die in de praktijk op Arm zichtbaar zijn.

# Contents

| A               | cknov                    | vledgements                                       | 4  |  |  |  |

|-----------------|--------------------------|---------------------------------------------------|----|--|--|--|

| English Summary |                          |                                                   |    |  |  |  |

| N               | Nederlandse Samenvatting |                                                   |    |  |  |  |

| In              | trodu                    | ction                                             | 9  |  |  |  |

| 1               | Background               |                                                   |    |  |  |  |

|                 | 1.1                      | Axiomatic Weak Memory By Example                  | 25 |  |  |  |

|                 | 1.2                      | Axiomatic Weak Memory, Formally                   | 28 |  |  |  |

|                 | 1.3                      | Axiomatic Weak Memory Architecture Semantics      | 33 |  |  |  |

|                 | 1.4                      | High-Level Theorem Statement                      | 42 |  |  |  |

| Ι               | Bina                     | ry Translation                                    |    |  |  |  |

| 2               | Stati                    | c Program Translation with Mapping Schemes        | 45 |  |  |  |

|                 | 2.1                      | Introduction                                      | 45 |  |  |  |

|                 | 2.2                      | Background                                        | 46 |  |  |  |

|                 | 2.3                      | Motivation                                        | 46 |  |  |  |

|                 | 2.4                      | Overview                                          | 47 |  |  |  |

|                 | 2.5                      | LIMM Weak Memory Model                            | 48 |  |  |  |

|                 | 2.6                      | Mapping Schemes                                   | 49 |  |  |  |

|                 | 2.7                      | Implementation                                    | 56 |  |  |  |

|                 | 2.8                      | Evaluation                                        | 57 |  |  |  |

|                 | 2.9                      | Conclusion                                        | 57 |  |  |  |

| 3               | Dyn                      | Dynamic Program Translation with Mapping Schemes  |    |  |  |  |

| _               | 3.1                      | Introduction                                      | 59 |  |  |  |

|                 | 3.2                      | Background                                        | 61 |  |  |  |

|                 | 3.3                      | Motivation                                        | 62 |  |  |  |

|                 | 3.4                      | Overview                                          | 66 |  |  |  |

|                 | 3.5                      | TIMM Weak Memory Model                            | 67 |  |  |  |

|                 | 3.6                      | Mapping Schemes                                   | 68 |  |  |  |

|                 | 3.7                      | Implementation                                    | 72 |  |  |  |

|                 | 3.8                      | Evaluation                                        | 73 |  |  |  |

|                 | 3.9                      | Conclusion                                        | 73 |  |  |  |

| 4               | Hyb                      | Hybrid Program Translation with Mapping Schemes 7 |    |  |  |  |

| •               | 4.1                      | Introduction                                      | 75 |  |  |  |

|                 | 4.2                      | Background and Motivation                         | 77 |  |  |  |

|                 | 4.3                      | Overview                                          | 79 |  |  |  |

|                 | 4.4                      | AIMM Weak Memory Model and Mapping Schemes        | 80 |  |  |  |

|                 | 4.5                      | Evaluation                                        | 83 |  |  |  |

|                 | 4.6                      | Conclusion                                        | 84 |  |  |  |

|                 |                          |                                                   |    |  |  |  |

| В11              | nary I                                 | Translation Related Work                | 85  |  |

|------------------|----------------------------------------|-----------------------------------------|-----|--|

|                  | Conc                                   | currency Semantics                      | 85  |  |

|                  | Bina                                   | ry Translation                          | 87  |  |

| тт               | D                                      | (Madagiantian                           |     |  |

| II               | Proof Mechanization                    |                                         |     |  |

| 5                |                                        | k Memory Mapping Proofs in Agda         | 88  |  |

|                  | 5.1                                    | Introduction                            |     |  |

|                  | 5.2                                    | Background                              |     |  |

|                  | 5.3                                    | Weak Memory Mechanization               | -   |  |

|                  | 5.4                                    | Mapping Proof Mechanization             |     |  |

|                  | 5.5                                    | Case Study: Mapping x86 to Arm          |     |  |

|                  | 5.6                                    | Related Work                            | 104 |  |

|                  | 5.7                                    | Conclusion                              | 105 |  |

| Ш                | Dvna                                   | amic Analysis                           |     |  |

| 6                | Porting Programs with Dynamic Analysis |                                         |     |  |

| Ü                | 6.1                                    | Introduction                            |     |  |

|                  |                                        | Background                              |     |  |

|                  | 6.3                                    | Operational-Axiomatic Weak Memory Model |     |  |

|                  |                                        | Robustness Analysis                     | _   |  |

|                  | 6.4                                    | Robustness Enforcement                  |     |  |

|                  | 6.5<br>6.6                             | Experimental Evaluation                 |     |  |

|                  |                                        | •                                       | _   |  |

|                  | 6.7                                    | Related Work                            |     |  |

|                  | 6.8                                    | Conclusion                              | 128 |  |

| 7                | Conclusion 129                         |                                         |     |  |

|                  | 7.1                                    | Future Work                             | 132 |  |

| Ac               | ronyr                                  | ms                                      | 133 |  |

| Bibliography     |                                        |                                         |     |  |

|                  |                                        |                                         |     |  |

| Curriculum Vitae |                                        |                                         |     |  |

# Introduction

Modern computing is concurrent, where multiple CPU cores execute a specific task *together*, while communicating through shared memory. Unfortunately, reasoning about a concurrent program is challenging because it behaves non-deterministically – which means its behavior could differ when executing again. Non-determinism appears when program threads interleave arbitrarily. In addition, when a program executes on computer hardware, more *weak* behaviors may non-deterministically appear that cannot be explained by thread interleaving. Those weak behaviors could occur when instructions execute out-of-order—to increase throughput—or when changes to shared program state do not immediate synchronize between threads.

Additionally, computer architectures differ, causing programs to show different non-deterministic behaviors when executing on different architectures. If we naively translate a program between two architectures without considering those weak behaviors, the resulting program could show unforeseen behaviors that never appeared on the original architecture. That difference between architectures thus poses a challenge when translating any program written for one architecture to another, while that translation is crucial to ensure the program's longevity across changes in the hardware landscape. This thesis addresses that challenge by formally reasoning about translating concurrent programs between weak memory computer architectures.

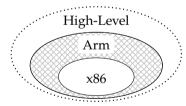

Concurrency on Computer Architectures. The observable weak behaviors vary between architectures. For instance, the predominant x86 (Owens et al., 2009) and Arm (Alglave et al., 2021) architectures show different weak behaviors, as illustrated in Figure 1. Therefore, translating a program from x86 to Arm is prone to errors, as it may unexpectedly introduce additional weak behaviors with new program outputs.

Figure 1: *Problem Illustration*. A concurrent program written in a high-level language may show one of many different behaviors, but *only a subset* of those appears on x86. When recompiling to Arm, unforeseen behaviors –that were not observed on x86– suddenly appear.

When we only have the compiled x86 program, but not the original source code, we do not know which additional behaviors were allowed by that source. However, even when we do have its source code in a high-level programming language, it could *implicitly* rely upon characteristics specific to the computer architecture used during development; for instance, when its developers only considered that one architecture or never tested on others. Upon recompiling to another architecture, such as Arm, that same program may suddenly show weak behaviors and outputs that were not observed before on x86.

**Formal Reasoning**. Although a program may behave non-deterministically, meaning its behavior differs between executions, those behaviors are *not arbitrary*. Any architecture preserves some order among instructions, described in a *formal semantics* of its *memory consistency model*. Those semantics mathematically describe the order among operations on all program threads, when executed on its corresponding architecture. Any processor implementing that architecture must follow its corresponding memory consistency model. With *formal reasoning* we refer to a *mathematically rigorous* approach to specifying and analyzing those weak memory semantics.

Through rigorous inspection of semantics, we can ensure programs behave as intended in all situations. By extension, analyzing program semantics often helps improve program *performance*. When ignoring semantics, we cannot be certain whether a particular transformation is correct. We might thus cautiously avoid it, hoping not to introduce errors but also miss out on its optimization opportunities. In contrast, when we know those semantics, we can judiciously pick any correct transformation, among which we can select the optimal one.

#### WEAK MEMORY EXAMPLE

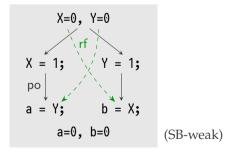

To illustrate the challenges of concurrent programming, consider the program below. It has two threads, with global variables X and Y, initialized to  $\emptyset$  and shared between the threads, while A and A are local to the right thread. The left thread A passes A messages by writing A to A and A, which the right thread reads in reverse order.

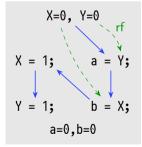

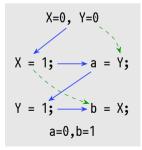

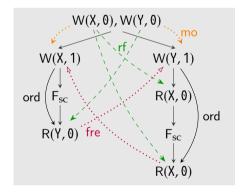

When considering only thread interleaving, corresponding to *sequential consistency* (Lamport, 1979), we perceive a global order between operations that preserves their order within each thread; instructions do no execute out-of-order but threads interleave arbitrarily. For instance, three such orders are shown with solid blue arrows:

Depending on the interleaving at runtime, different assignments to X and Y precede their observation by b and a. We relate those write and read operations to X and Y with the *reads-from* (rf) dashed green arrows. For instance, in the first two execution, a reads Y's initial value 0 because it is not yet overwritten. In contrast, in the right-most execution, a observes the value of Y after it is assigned 1.

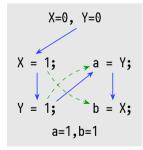

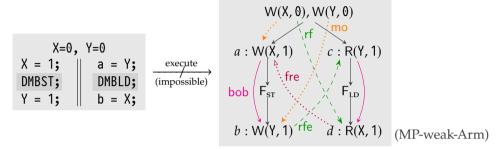

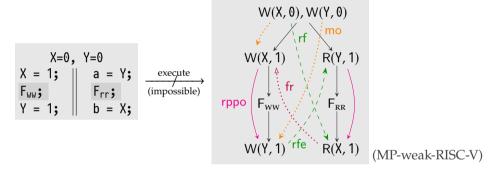

**Weak Behavior**. Most computer architectures show additional *weak* behaviors where the order among operations within a thread is not preserved. For our Message-Passing program, we could thus observe both threads executing its operations in reverse, as the following diagram demonstrates with the solid <u>blue</u> arrows:

The rf arrows point from written values to subsequent reads from the same locations along the global order. We thus reach the final assignment where a=1 and b=0. Crucially, that outcome is *impossible* when threads only interleave. Only when instructions execute out-of-order can we observe this outcome, making it a *weak* behavior.

The MP-weak behavior is observable on Arm (Alglave et al., 2021), but not on x86 (Owens et al., 2009). As these architectures have different weak memory models, they preserve different orders within each thread. Arm reorders the write-write pair on the first thread and the read-read pair on the second; either reordering alone could also produce the weak outcome. Those pairs *cannot* reorder on x86, making this behavior impossible on x86. If we had naively translated the program from x86 to Arm, the MP-weak behavior with outcome a=1,b=0 could unexpectedly appear.

**Robustness**. Although Arm preserves the order among fewer memory operations than x86, it provides memory primitives to *explicitly* order them. For instance, we can place *fences* in our Message-Passing program as follows:

| Arm    |        |  |  |  |  |  |

|--------|--------|--|--|--|--|--|

| X=0, Y | =0     |  |  |  |  |  |

| X = 1; | a = Y; |  |  |  |  |  |

| DMBFF; | DMBFF; |  |  |  |  |  |

| Y = 1; | b = X; |  |  |  |  |  |

An Arm DMBFF fence, short for "Data Memory Barrier Full Fence", explicitly prevents memory operations from reordering across it. In particular, as operations no longer reorder, the MP-weak outcome is not possible anymore. For this program, we have restricted its behaviors on Arm to those on x86 – known as enforcing x86-Arm *robustness* (Chakraborty, 2021; Bouajjani et al., 2013a). When executing an x86-Arm robust program on Arm, it shows only those behaviors also observable on x86.

When migrating programs from x86 to Arm, we must enforce x86-Arm robustness to prevent new weak behaviors from appearing. A simple approach inserts

DMBFF fences between *all* adjacent memory accesses – thus enforcing sequential consistency. However, fences incur a runtime overhead (Liu et al., 2020), which varies with their location in the program and the complexity of CPU-specific bus architecture. In any case, runtime performance benefits from placing them judiciously.

#### PROBLEM STATEMENT

Translating programs between architectures is important in practice, as the landscape of computing hardware has evolved within the last decade, with a shift from the dominating x86 architecture (Intel Corporation, 2025) to new Instruction Set Architectures (ISAs), such as Arm (Arm Limited, 2024) and RISC-V (RISC-V International, 2024). Arm CPUs are now widely deployed, on both consumer and enterprise hardware, for instance, with Apple's M3 (Apple Inc., 2023), Google Axion (Vahdat, 2024), AWS Graviton (Stormacq, 2022), and Microsoft Cobalt (Kishan and Borkar, 2024). When naively translating legacy x86 programs to Arm, they could unexpectedly show new weak behaviors, of which MP-weak is an example. We thus ask:

#### Research Question

How can we correctly translate programs between weak memory model architectures while minimizing performance overhead?

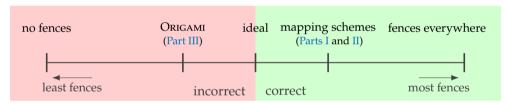

We approach this problem from multiple angles, each with its own correctness and performance characteristics. The primary contexts within which we consider this problem are *binary translation with mapping schemes* and by *dynamic program analysis*.

Binary Translation with Proven Mapping Schemes. When the source code of the legacy program –or a part of it– is no longer available or when it contains architectural intrinsics, it cannot simply be recompiled. *Binary translation* addresses this problem by translating the compiled binary program (*e.g.*, from x86) to another architecture (*e.g.*, to Arm). That translation process should be fast, as it takes place shortly before executing the program and thus directly affects the time needed to execute the program to completion. Hence, a binary translator often cannot afford to thoroughly analyze the program. Instead, we aim to define *mapping schemes*, which translate programs instruction-by-instruction. These mapping schemes should be *correct in general*, for any program with any number of threads, but also minimize performance overhead. In particular, our correctness criterion concerns *robustness*, where the mapped program must not show additional weak behaviors on the new architecture – about which we thus ask:

## Sub-Question 1

How can we define performant *mapping schemes* between weak memory model architectures and prove these preserve robustness?

**Dynamic Program Analysis**. Although the mapping schemes are a *general* solution, useful when we *cannot* analyze the program, they are often not optimal for a *specific* program. However, when we know the program, we could analyze it to place fewer fences that still enforce robustness. In particular, we can fix only those violations that appear in program traces when simulating its execution – about which we ask:

#### Sub-Question 2

How can we detect and fix robustness violations that appear in program traces?

#### DISSERTATION STRUCTURE

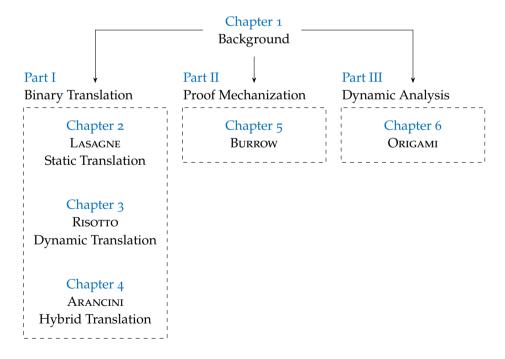

We answer our research questions in the main chapters of this dissertation, which are based on five papers. The presentation within those papers differs from this dissertation. Although the articles are internally complete, their background and formal definitions overlap considerably, and are thus extracted into "Chapter 1 – Background". We visualize the relation between the chapters as follows:

For the papers included in Part I, I am *co-lead* author and was responsible for the formal semantic models, mappings, transformations, and mechanized proofs. Within this dissertation, contributions of my collaborators are reduced.

The remainder of this introduction summarizes the parts with their corresponding chapters. In Part I we propose novel formal weak memory models for various binary translation systems, with mapping schemes to translate from x86 to Arm and RISC-V, each accompanied by mechanized proofs in Agda (Agda Team, 2025a). Through this formalization, we identified errors in existing memory models and program translators. Notably, we propose a fix to the Arm memory model in Chapter 3. In Part II we elaborate on the proof engineering challenges we faced when mechanizing the proofs for our mapping schemes in Part I and propose a general approach to simplify writing such proofs in Agda. Finally, in Part III we introduce an alternative method to enforce x86-Arm robustness by dynamically analyzing any program to fix only those violations that it actually observes at runtime.

#### PART I: BINARY TRANSLATION

In part I we look at *binary translation*, where we translate compiled binary programs from one architecture to another. The contained Chapters 2 to 4 present different approaches to translate binary programs, each with its own challenges. Before going into their individual challenges, we explain their shared context and background.

With binary translation we face the robustness challenges as explained above, but *additionally* require the translation itself to be fast because it takes place shortly before executing the program. That requirement rules out existing approaches that thoroughly analyze the program to enforce robustness (Chakraborty, 2021; Bouajjani et al., 2013a; Alglave et al., 2017), which are too computationally demanding within binary translators.

**Mapping Scheme**. Our approach enforces x86-Arm robustness with *mapping schemes* that translate x86 memory instruction-by-instruction to Arm with appropriate fences. On page 11 we showed an example where we added *full* DMBFF fences between adjacent instructions for the Message-Passing program. However, that approach would order many Arm programs *stronger* than the original x86 program, unnecessarily harming the program's runtime performance.

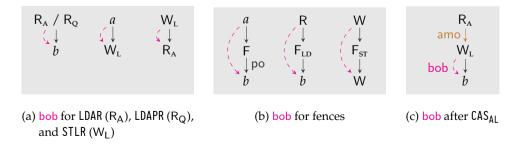

Instead, we can insert lightweight fences. While a full fence orders *any* memory accesses across it, Arm's load fence DMBLD orders only preceding loads with any succeeding accesses, while its store fence DMBST orders only stores across it. Those lightweight fences incur a lower runtime overhead than full fences (Liu et al., 2020), but can preserve x86-Arm robustness when placed correctly. We thus define a mapping scheme resembling the following, which is simplified for presentation:

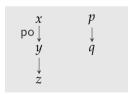

| x86 |               | Arm      |

|-----|---------------|----------|

| ld  | $\rightarrow$ | ld;DMBLD |

| st  | $\rightarrow$ | DMBST;st |

<sup>&</sup>lt;sup>1</sup>RMW and fence instructions are omitted.

When translating from x86 to Arm, we place a load fence after every load instruction (ld) and a store fence before every store instruction (st). However, we can only know the mapping scheme is correct by ensuring any behavior of the resulting Arm program was also observable for original x86 program. Hence, we need to carefully inspect the weak memory semantics of both architectures (Owens et al., 2009; Alglave et al., 2021) to formally prove our mapping scheme correct. For the chapters in part I, we developed mapping schemes for various binary translators, with corresponding mechanized proofs in the Agda proof assistant (Agda Team, 2025a).

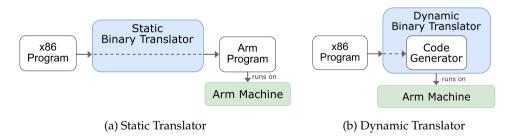

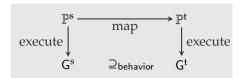

**Static vs. Dynamic Binary Translation**. In Chapters 2 to 4, we develop such mapping schemes for three different binary translators, whose system architectures differ. Binary translators are often either *static*, which translate the entire program *before* running it, or *dynamic*, which translate it *while* running. Figure 2 illustrates those architectural differences. Either approach has its own strengths and weaknesses. By translating a program before execution, a static translator can apply whole-program optimizations, benefiting performance. However, static translation is undecidable in general (Rice, 1953) –meaning a static binary translator that can translate every program *cannot exist*– because much semantic information was lost during compilation (Andriesse et al., 2016). In contrast, by translating the program while executing, a dynamic binary translator does not need to recover all information beforehand—which is impossible in general—and thus only recovers the information needed in its specific runtime context. Unfortunately, that runtime translation often incurs a greater performance overhead than static translation. Finally, a *hybrid* binary translator has characteristics of both static and dynamic, thus gaining benefits from both.

Figure 2: High-level Architectures of Binary Translators. In either case, the objective is to execute an x86 program on Arm, but the approaches differ. A static translator translates the entire program, which then executes on the Arm machine. In contrast, a dynamic translator continuously translates program *fragments* "just-in-time", as they are encountered at runtime.

We will now explain the individual contributions of the chapters in part I.

# Chapter 2: Static Program Translation with Mapping Schemes

Based on "Lasagne: A Static Binary Translator for Weak Memory Model Architectures" by Rodrigo Rocha\*, Dennis Sprokholt\*, Martin Fink, Redha Gouicem, Tom Spink, Soham Chakraborty, Pramod Bhatotia, at PLDI 2022 (\* = co-lead authorship)

Chapter 2 introduces our *static* binary translator Lasagne, which builds upon the LLVM compiler framework (Lattner and Adve, 2004) and mctoll lifter (Yadavalli and Smith, 2019), which *lifts* x86 binary programs to the LLVM Intermediate Representation (IR). Lifting aims to reverse the compilation process from LLVM IR to x86 through which the original x86 binary program was produced. After lifting the programs, it naturally uses LLVM's existing compilation backend to produce the final Arm binary program. We identified robustness errors in the existing translation by LLVM and mctoll, which we fixed in Lasagne with our formally verified mapping scheme.

We first define a formal LLVM IR Concurrency Memory Model (LIMM), which is intermediate within the mapping scheme. As an example, the simplified variant of our mapping scheme becomes:

Within our memory model and mappings we also carefully consider Read-Modify-Write (RMW) operations, which atomically read and write to shared memory. An RMW fails when another thread concurrently writes to the same memory location. The success case may enforce subtly different orders from the failure case, depending on the ISA. Additionally, while x86 has single-instruction RMW instructions, on Arm these are often implemented with two separate –but connected–load-linked store-conditional (ll/sc) instructions, which also order weaker (Pulte et al., 2017; Alglave et al., 2014). Our mapping scheme correctly translates x86's RMW to Arm's corresponding instructions, for both the success and failure cases, by placing appropriate fences.

# Chapter 3: Dynamic Program Translation with Mapping Schemes

Based on "Risotto: A Dynamic Binary Translator for Weak Memory Model Architectures"

by Redha Gouicem\*, Dennis Sprokholt\*, Jasper Ruehl, Rodrigo Rocha, Tom Spink, Soham Chakraborty, and Pramod Bhatotia, at ASPLOS 2023 (\* = co-lead authorship)

Recipient of an ASPLOS Distinguished Artifact Award

Chapter 3 introduces our *dynamic* binary translator RISOTTO, which builds upon the existing QEMU dynamic binary translator (Bellard, 2005; QEMU Team, 2003). QEMU internally uses its Tiny Code Generator (TCG), with TCG IR language. QEMU does not officially support strong-on-weak ISA execution, such as running x86 programs on Arm.

We observed QEMU's existing translation attempts to enforce a *stronger* ordering than x86 when executing on Arm, unnecessarily hurting performance (Liu et al., 2020). Despite those attempts, it still fails to translate programs correctly, as we discovered several translation errors. We eliminate those errors by defining the first formal weak memory model of TCG IR, called TIMM, and proving the mappings correct from x86 to TCG IR to Arm. We replaced the existing erroneous mappings in QEMU with our verified mappings. Additionally, we proved several optimizations correct on TCG IR, such as memory access eliminations, which commonly appear in TCG's constant propagation and folding passes, as well as various reordering optimizations.

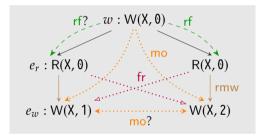

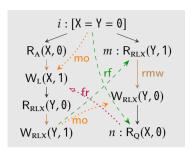

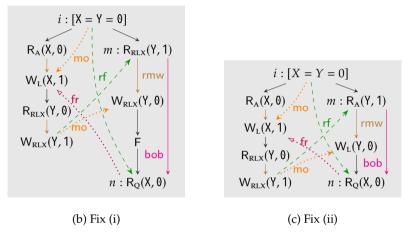

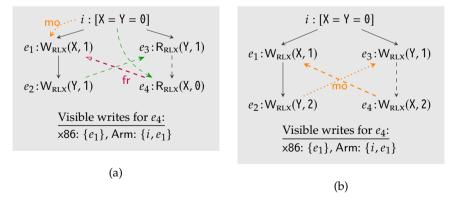

We also proved our translations correct with respect to a newer Arm model (Alglave et al., 2021) than we did for Lasagne (Chapter 2). This new model specifically includes formal semantics for a new Arm "Compare and Swap Acquire Release" CAS<sub>AL</sub> instruction, which is a *single-instruction* RMW operation, unlike Arm's prior ll/sc pair. That new CAS<sub>AL</sub> aims to "act as a full barrier" (Alglave et al., 2021, p.18), like x86's RMW. However, through our formal proofs we discovered that it orders weaker than a full barrier! To correctly translate x86 programs, we thus must either (*i*) place strong fences around the CAS<sub>AL</sub>, like we did with ll/sc pairs in Chapter 2, thus harming performance; or (*ii*) strengthen the Arm model. As the former option would invalidate the advantage of CAS<sub>AL</sub> over ll/sc, we prefer the latter, for which we propose a fix to the Arm model. After reporting the error to the authors, they included an equivalent strengthening (Alglave, 2022).

### Chapter 4: Hybrid Program Translation with Mapping Schemes

Based on "Arancini: A Hybrid Binary Translator for Weak Memory Model Architectures"

by Sebastian Reimers\*, Dennis Sprokholt\*, Martin Fink, Theofilos Augoustis, Simon Kammermeier, Rodrigo Rocha, Tom Spink, Redha Gouicem, Soham Chakraborty, and Pramod Bhatotia (\* = co-lead authorship)

Chapter 4 introduces our *hybrid* binary translator Arancini. Static translators cannot translate all programs (Andriesse et al., 2016) because semantic information was lost when compiling the original program, which cannot be recovered in general (Rice, 1953). For instance, lifting compiled C++ programs is challenging as they commonly use dynamic dispatch, where jump targets are known only at runtime, which we often cannot recover statically. In contrast, dynamic translation can translate any program but incurs a performance overhead at runtime because the translation happens during program execution. Through hybrid translation, Arancini gains the benefits of both. Arancini translates much of the program statically, thus avoiding the runtime performance overhead, while resorting to dynamic translation whenever static translation is impossible.

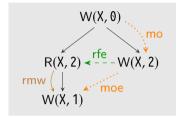

Again, we define and prove mapping schemes that extend upon Lasagne (Chapter 2) and Risotto (Chapter 3) in *two* ways: (*i*) by translating *mixed-size* accesses (Flur et al., 2017; Alglave et al., 2021) from x86 to Arm, which access memory in units of multiple size (*e.g.*, 1/2/4/8-byte units); and (*ii*) by translating x86 to RISC-V (RISC-V International, 2024). For Arancini we define AranciniR, a custom IR with corresponding weak memory model AIMM, resembling Lasagne's LIMM and Risotto's TIMM models but additionally includes semantics for mixed-size accesses.

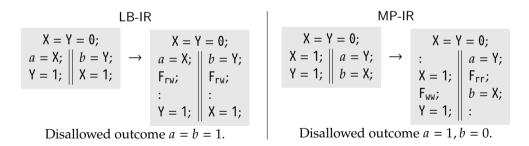

During our proof efforts, we discovered *splitting transformations* are incorrect. For instance, it is incorrect to split a 16-bit store operation into two separate 8-bit stores, as the example demonstrates below. The 16-bit variable X –initially  $\emptyset$ – consists of two adjacent 8-bit variables  $X_H$  and  $X_L$ , denoting X's most and least significant byte, respectively.

While the original program *cannot* show a terminal state with X=0x1234 and a=0x34, the split erroneously introduces that unforeseen behavior; when the second thread executes entirely in-between the instructions on the first thread. As the error already appears when only interleaving threads, it also appears in any weaker memory model.

#### PART II: PROOF MECHANIZATION

Part I has introduced the formal memory models for the languages inside our binary translators, with mapping proofs between architectures and optimization proofs. As the formal axiomatic weak memory models we used are often large and complex, writing such proofs requires inspecting many cases with subtle complexities that are often error-prone (Batty et al., 2016; Manerkar et al., 2016; Sarkar et al., 2012, 2011). To avoid missing proof cases, we *mechanized* their proofs in the Agda proof assistant (Agda Team, 2025a), significantly increasing their reliability.

The proofs for Lasagne, Risotto, and Arancini independently consist of *thousands* of lines of Agda, making them large and especially *rigid* code bases. As with any large computer program's source code, there are many ways to structure the code, some more maintainable than others. Throughout our proof engineering efforts for mapping schemes, we tried numerous proof structures to reduce their complexity and increase maintainability. Within part II, we present the results of those efforts.

# Chapter 5: Weak Memory Mapping Proofs in Agda

Based on "Mechanizing Weak Memory Proofs in Agda" by Dennis Sprokholt and Soham Chakraborty

Chapter 5 introduces our Agda proof framework Burrow to *mechanize* axiomatic weak memory semantics and prove corresponding transformations correct. Although existing approaches bring significant theoretical contributions – for instance, by finding errors in existing models (Chakraborty and Vafeiadis, 2016, 2017), repairing those models (Lahav et al., 2017), or introducing new models (Batty et al., 2011; Kang et al., 2017) – writing the corresponding mechanized proofs remains time-consuming for proof engineers. Burrow reduces those proof mechanization challenges with custom primitives and abstractions that are specific to the domain of weak memory transformation proofs.

Burrow leverages Agda's specific strengths, which differ from those of other proofs assistants. Whereas idiomatic Rocq (Bertot and Castran, 2010) favors extensive use of *tactics* to automatically solve goals, Agda's explicit term manipulation with dependent pattern matching (Coquand, 1992; Cockx and Abel, 2018) and easy syntax extension –but lack of tactics– emphasizes using the right formalization abstractions. In particular, we define domain-specific proof primitives, with which Burrow proves large fragments of weak memory transformation proofs *generally*.

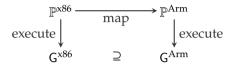

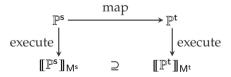

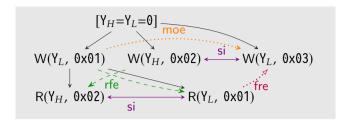

We first define the high-level theorem, which all our proofs follow. For the Message-Passing example on page 10, we saw that a program may show one of multiple executions, depending on thread interleaving and out-of-order execution. However, Arm can show the MP-weak behavior, which x86 does not. If we had naively translated the program from x86 to Arm, that additional behavior would suddenly appear, which is incorrect. Instead, we must ensure that any behavior observed when

executing the target program  $\mathbb{P}^{Arm}$ , was also a behavior the source program  $\mathbb{P}^{x86}$ , which we can visualize below.  $G^{x86}$  denotes the set of behaviors of the source program  $\mathbb{P}^{x86}$ , while  $G^{Arm}$  denotes the set of behaviors of the target program  $\mathbb{P}^{Arm}$ .

After defining this proof structure in Agda, we define its components, which ensure executions are well-formed and consistent with their architecture's weak memory semantics. This same structure applies when proving optimizations correct.

Next, we identify and clarify ambiguities in general weak memory model definitions. Although they are formal models, much of their definitions are given only *implicitly*. While pen-and-paper proofs may permit unspecific or ambiguous definitions, mechanized proofs demand meticulous specification of all details. The mechanized Agda definitions thus precisely capture the weak memory semantics. Using those definitions, Burrow provides several mapping primitives and abstractions with which programmers only need to *define* the mapping between architectures and prove that they preserve several simple properties. Burrow then produces large fragments of the weak memory proofs generally, allowing proof engineers to focus only on the interesting parts.

We demonstrate Burrow's effectiveness by proving the conjectured mapping from x86 to Arm by Alglave et al. (2021, §2.5), which is only true after fixing the Arm model (Alglave, 2022), as discussed in Chapter 3. Their mapping differs from ours (Chapters 2 to 4), as ours insert fences around memory accesses, while theirs annotate accesses with memory orders – which is an alternative method to preserve memory orders on Arm. We prove their alternative mapping as a case study to demonstrate Burrow's versatility.

#### PART III: DYNAMIC ANALYSIS

In part I and II we looked at mapping schemes to enforce x86-Arm robustness. The advantage of mapping schemes is that they are correct *for any program* and require no expensive program analysis to determine fence placement, which was crucial for the binary translators in part I. However, their primary disadvantage is that they may insert excessively many fences, which we could avoid when we know the specific program. In part III we aim to analyze any program to enforce memory orders only when needed.

### Chapter 6: Porting Programs with Dynamic Analysis

Based on "Porting Concurrent Programs between Weak Memory Architectures" by Dennis Sprokholt, Anish Yogesh Kulkarni, Yifan Song, S. Krishna, and Soham Chakraborty, under submission

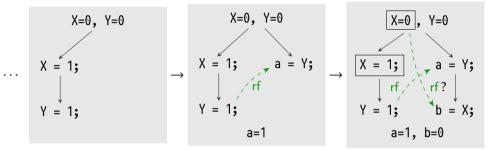

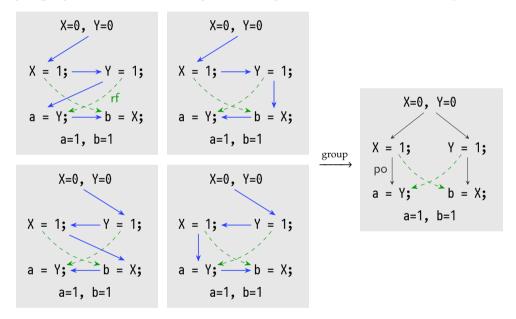

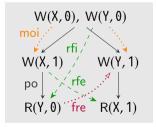

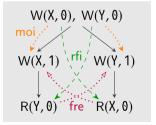

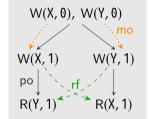

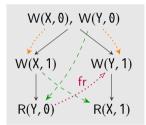

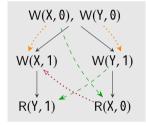

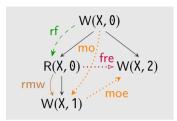

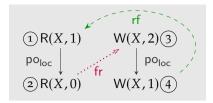

Chapter 6 introduces our dynamic program analyzer Origami, which identifies x86-Arm robustness violations by simulating programs step-by-step under both the x86 and Arm memory model, reporting mismatching steps. Consider again the Message-Passing program, where the order of instructions is preserved on both threads in x86, but on Arm they can reorder. We construct one execution step-by-step, where at every step we select the next instruction to execute at random, shown after the first *two* steps:

Unlike with the previous execution examples (on page 10), where we showed a *global* blue order among events, we now only show the black *program order* (po) arrows among operations *within each thread*. Upon appending the final read operation from X, we must select a write operation that it reads-from (rf). As the preceding operation on the second thread already observed the value 1 being written to Y, it established a causal order between them on x86. On Arm, the operations on both threads can freely reorder, making it possible to observe X=0 in the final read operation. In contrast, x86 *cannot* observe that value, as it is "hidden behind" the assignment X=1. Hence, we have discovered a robustness violation, where Arm shows the additional behavior where A=1, A=0, which is impossible on x86. That violation is the same as the MP-weak execution seen before.

To analyze programs step-by-step, we first define an operational-axiomatic weak memory semantics for x86 and Arm, based on existing axiomatic semantics (Owens et al., 2009; Alglave et al., 2014, 2017). These semantics formally define the valid program steps in both architectures. Using those semantics we define an x86-Arm robustness analysis algorithm, which repeatedly takes a step in both models at random. We implement the analysis algorithm in Origami, which builds upon C11Tester (Luo and Demsky, 2021) to randomly explore program executions. Upon encountering a robustness violation, C11Tester reports the program trace that produced it.

After discovering a robustness violation, we need to fix it. As part of Origami, we define another robustness *enforcement* algorithm, which identifies all weak paths

leading to the violation. For instance, in the above example, it identifies the black po edges between the operations in both threads. As those operations are ordered in x86 but not in Arm, the orders on both threads must be strengthened on Arm, for instance, by inserting fences. To do that, our enforcement algorithm proposes minimal strengthenings to prevent a given robustness violation from appearing again.

After several iterations of analysis and enforcement, Origami finds no further robustness violations. In contrast to existing model checkers (Abdulla et al., 2015a,b; Bouajjani et al., 2013a; Oberhauser et al., 2021), whose *exhaustive* exploration of the program's state space often does not scale, Origami's random exploration makes it very suitable for large programs. Unfortunately, either approach may miss violations: Model checkers miss violations beyond their reachable scale, while Origami misses those unexplored by its random process. However, we experimentally demonstrate that Origami identifies many x86-Arm robustness violations in existing benchmark programs (Luo and Demsky, 2021; Chakraborty, 2021) while inserting fewer fences than our mapping schemes (Chapters 2 to 4), benefiting the program's runtime performance.

#### **PAPERS**

The work presented in this dissertation is also included in the following papers (not all of which are published), listed in reverse chronological order:

# Mechanizing Weak Memory Proofs in Agda

Dennis Sprokholt, Soham Chakraborty

# Porting Concurrent Programs between Weak Memory Architectures

Dennis Sprokholt, Anish Kulkarni, Yifan Song, S. Krishna, Soham Chakraborty

# Arancini: A Hybrid Binary Translator for Weak Memory Model Architectures

Sebastian Reimers\*, <u>Dennis Sprokholt</u>\*, Martin Fink, Theofilos Augoustis, Simon Kammermeier, Rodrigo Rocha, Tom Spink, Redha Gouicem, Soham Chakraborty, Pramod Bhatotia

# Risotto: A Dynamic Binary Translator for Weak Memory Model Architectures

Redha Gouicem\*, <u>Dennis Sprokholt</u>\*, Jasper Ruehl, Rodrigo Rocha, Tom Spink, Soham Chakraborty, Pramod Bhatotia (ASPLOS 2023)

TRecipient of an ASPLOS Distinguished Artifact Award

## Lasagne: A Static Binary Translator for Weak Memory Model Architectures

Rodrigo Rocha\*, <u>Dennis Sprokholt</u>\*, Martin Fink, Redha Gouicem, Tom Spink, Soham Chakraborty, Pramod Bhatotia (PLDI 2022)

During my PhD research I have also collaborated on the following papers, which are *not* included in this dissertation:

## **Distributing Time-Affected Compute-Intensive Programs**

Dennis Sprokholt, Soham Chakraborty

#### Cage: Hardware-Accelerated Safe WebAssembly Programs

Martin Fink, Dimitrios Stavrakakis, <u>Dennis Sprokholt</u>, Soham Chakraborty, Jan-Erik Ekberg, Pramod Bhatotia (CGO 2025)

<sup>\* =</sup> co-lead authorship

#### **TOOLS AND PROOFS**

All our tools and proofs are available as open-source software.

- Lasagne (Chapter 2)

- Proofs Q github.com/binary-translation/lasagne-proofs

- RISOTTO (Chapter 3)

- Proofs Ggithub.com/binary-translation/risotto-proofs

- Arancini (Chapter 4)

- Proofs Q github.com/sourcedennis/arancini-proofs

- Burrow (Chapter 5)

- Burrow ♥ github.com/sourcedennis/agda-burrow

- Dopo Q github.com/sourcedennis/agda-dodo

- Case Study Q github.com/sourcedennis/armed-proofs

- Origami (Chapter 6)

- Robustness Analysis Q github.com/sourcedennis/c11tester-x86-arm

- Robustness Enforcement Q github.com/sourcedennis/enforce-robustness

- Custom Fency Programs Q github.com/sourcedennis/fency-programs

# Chapter 1

# Background

In this chapter, we introduce weak memory consistency semantics, which we use in the remaining chapters. First, in Section 1.1 we explain *by example* the subtle behaviors that appear on weak memory architectures. Second, in Section 1.2 we introduce the formal notations for axiomatic weak memory models, which we later use to formalize weak memory behaviors. Third, in Section 1.3 we cover established weak memory models of existing ISA architectures, such as x86, Arm, and RISC-V. Finally, in Section 1.4 we give the high-level structure of the theorems we consider in the remaining chapters, which captures the correctness criterion of transformations involving concurrency primitives.

#### 1.1 AXIOMATIC WEAK MEMORY BY EXAMPLE

We first introduce axiomatic weak memory semantics by example. On page 10 we already showed the Message-Passing program, whose behavior differs between x86 and Arm. Here, we give another program, which shows *the same* weak behavior on x86 and Arm. The program again has two threads, where X and Y are shared between them and are initialized to 0, while a and b are thread-local to their respective threads:

This program is commonly known as the Store-Buffering program because some architectures *buffer the stores* (Sewell et al., 2010), thus not immediately communicating written values to other CPU cores, resulting in weak behaviors. Before going into those weak behaviors, we look at the behaviors that emerge *only* from interleaving, which thus respect the instruction ordering within each thread. For instance, we may non-deterministically observe one of the following interleaving orders, marked with blue *solid* arrows:

Although the order among instructions within each thread is preserved in the above

executions, the threads interleave arbitrarily. The green dashed *reads from* (rf) arrows relate write operations to the subsequent same-location read operation in the interleaving order. Depending on the specific interleaving, those read operations observe a value written by a different write operation, resulting in distinct assignments to a and b upon termination. Note that the outcome a=0, b=0 is *impossible* under sequential consistency.

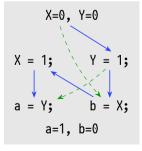

**Grouping Behaviors**. The previous examples explicitly showed a global runtime order among instructions with the blue arrows. Such global orders are easily defined when considering only interleaving. However, for weak behaviors on CPUs, defining a total order among events becomes challenging – for instance, when an instruction's effects are not immediately observable to other threads. To avoid that challenge altogether, we do *not* explicitly represent a global order among events, but group executions based on the runtime interactions between instructions. To illustrate that grouping, consider the following interleaving executions for Store-Buffering:

We see four distinct interleavings, where reading from X and Y observes the value written by the same respective write operation. Consequently, each results in the same final state where a=1 and b=1. For our purposes of modeling weak memory semantics, we need not distinguish between the specific interleavings, but only consider the rf relations between the instructions, which the rightmost grouped execution shows. In that execution, we do *not* model the blue global order, but only the thread-local *program order* (po) between the instructions and the reads-from (rf) edges between them. The program order captures the runtime order among instructions as they appeared in the program's syntax.

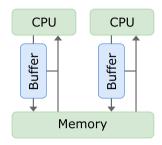

**Architectural Intuition**. For the Store-Buffering program we could observe weak behaviors when a microarchitecture has *store buffers* (Sewell et al., 2010). Conceptually, a store buffers is a FIFO queue residing at each CPU core containing the pending writes to main memory, as depicted in Figure 3. As writing to memory is time consuming, these buffers allow the CPU core to continue executing other instructions while delaying the writes to main memory until later.

Figure 3: A depiction of *store buffers*. When a CPU core writes a value, it initially remains in a local store buffer. Those buffered values only later flush to main memory, meaning other cores cannot immediately observe them. When reading a value, a CPU core only looks in main memory when the value is absent in its local store buffer.

Store buffers illustrate why it is challenging to determine an order between instructions at runtime. Executing a write instruction is not immediately visible to other threads, as a written value remains in a local buffer. Only at a later point does it propagate from that buffer to main memory. Micro-architecturally, executing a write instruction and then propagating that value to memory are independent actions, while they are a single instruction in the program syntax. If we had explicitly modeled those actions, the global order would have gotten excessively complex. Instead, we *don't* model a global order, but only consider whether an instruction's effects is observable to another – regardless of how that took place inside the CPU.

Weak Behavior. As a result of store buffers, we can observe a weak behavior for the Store-Buffering program. Consider the two CPU cores writing the value 1 to variables X and Y, but each remains locally in a store buffer. When the threads respectively read the values from Y and X—which is only kept in the opposing thread's store buffer—both retrieve the value  $\emptyset$  from main memory. The corresponding execution is:

Note again that we do not model a global order among instructions, but only relate the write instructions to read instructions that observe their values, regardless of how that happened within the microarchitecture. Crucially, observe that this behavior where a and b read 0 from Y and X, respectively, is *impossible* when only interleaving threads. That is, there *exists no* thread interleaving producing this behavior, meaning it is a *weak* behavior.

Architecture Behaviors. The SB-weak behavior of the Store-Buffering program is observable on both x86 (Owens et al., 2009) and Arm (Alglave et al., 2021). In contrast, the MP-weak behavior (on page 11) of Message-Passing is observable on Arm but *not* on x86. In general, Arm preserves fewer orders among regular memory accesses than x86 within each thread, making Arm a strictly *weaker* architecture. Although x86's weak behaviors can fully be described as a consequence of store buffers (Owens et al., 2009), Arm shows additional weak behaviors that cannot be explained only by store buffers (*e.g.*, the MP-weak). Those weak behaviors appear because Arm can execute many instructions out-of-order (Alglave et al., 2014).

The memory consistency semantics of a particular architecture or language are *defined by* the behaviors observable for any program. Although we gave several example behaviors for two programs, which vary between architectures, we require a more general mechanism to define behaviors for any program. We can only do that with a mathematically rigorous definition of these semantics, which we explain next.

#### 1.2 AXIOMATIC WEAK MEMORY, FORMALLY

The previous subsection gave intuitions and examples to illustrate the intricacies of weak memory concurrency. In this subsection we expand on those idea with the standard formal axiomatic weak memory semantics (Alglave et al., 2014; Batty et al., 2011), which restricts program behavior with axioms.

**Purpose of Semantics**. The purpose of formal semantics is to *mathematically* –without ambiguity– assign meaning to programs (Floyd, 1993). In particular, we consider *axiomatic semantics*, as originally coined by Hoare (1969), where we describe a program's behaviors with logical predicates. Crucially, semantics *only describe* program behaviors, which is *orthogonal* to their computational characteristics. Rice (1953) famously showed non-trivial semantic properties<sup>2</sup> are undecidable, meaning we cannot determine whether a given property holds for any program. In this section, we intend only to precisely describe the weak memory behaviors of programs.

### 1.2.1 Executions

Axiomatic weak memory semantics (Alglave et al., 2014; Batty et al., 2011) define the behavior of any program with *execution graphs*, each consisting of *events* and various *relations*. Each event is either a read (R), write (W), or fence (F) event. The R and W events have a location and value, for instance, R(X, 2) reads the value 2 from location X.

<sup>&</sup>lt;sup>2</sup> An example of a semantic property is whether a given program ever reads the value 1 from some location X. It is impossible to *decide* that for *all* programs.

Those memory locations are concrete values (*e.g.*, 0x12345678), but we denote them *symbolically* (*e.g.*, X and Y) in the examples, for clarity of presentation<sup>3</sup>. Those symbolic locations strictly represent *distinct* locations in memory (*i.e.*, X and Y are strictly different). Each event also has an identifier that is unique within the execution.

We capture various relations between events, of which we already gave po and rf by example in Section 1.1. We distinguish between *primitive* and *derived* relations. The latter follow entirely from the former, but serve as notational conveniences. The typical *primitive* relations are:

- Program order (po), relating events by their syntactic order: the order among instructions in the program text carries over to execution graphs with po edges. It is a total order per thread.

- Reads-from (rf), which relates a W event to the R event reading from it. Every R event reads-from exactly one W event. For instance, when event  $e_2$ : R(X, 1) reads 1 from location X, where that value was earlier written by  $e_1$ : W(X, 1), then we have an rf edge from  $e_1$  to  $e_2$ , alternatively denoted as rf( $e_1$ ,  $e_2$ ).

- Modification order (mo), which relates a W event with a W event overwriting it. For instance, when event  $e_3$ : W(X, 1) first writes 1 to location X, which event  $e_4$ : W(X, 2) then *overwrites* with 2, then we have an edge  $mo(e_3, e_4)$ . Both mo-related write events access the same location. Additionally, mo is a total order per location.

- Read-modify-write (rmw), relating the R and W of a successful atomic read-modify-write instruction (RMW). The RMW instructions are special instructions within architectures, where architectures can detect whether another thread modifies the written value in-between the atomic operation. The generated R and W events access the same location and are po-adjacent (*i.e.*, there are no po-intermediate events). We elaborate on these for various architectures in Section 1.3.

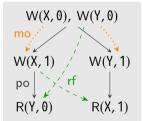

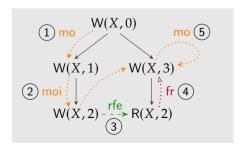

To illustrate those events and relations, we show two such execution graphs for the Store-Buffering program, consisting only of primitive relations.

Although the program syntax also contained thread-local variables **a** and **b**, those are omitted<sup>4</sup> in our semantics. After all, these executions aim to capture only the order

<sup>&</sup>lt;sup>3</sup>In contrast, in the mechanized proofs of Chapters 2 to 5 and analysis of Chapter 6, locations are concrete.

<sup>&</sup>lt;sup>4</sup>If we had wanted to capture the thread-local variables in the graphs, we could introduce additional shared variables A and B to which we write the values of the thread-local variables a and b.

among operations communicating through shared memory, which are X and Y for this program. The left execution captures a sequentially consistent behavior, resulting in a=0, b=1. The right execution captures a weak behavior, resulting in a=0, b=0.

The initial W events, which precede the start of all threads, capture the initial state of memory. In reality, that initial state was established before the program started -e.g., by preceding programs— and is beyond the program's semantics. We always initialize those values to  $\emptyset$  in visual execution graphs. Finally, note that we omit transitive edges (e.g., for po and mo) in the graphs for presentational clarity.

With the events and primitive relations, we define an execution:

▶ Definition 1 (Execution). We denote an execution as  $X \triangleq \langle E, po, rf, mo, rmw \rangle$ , where X.E is the set of events, X.po, X.rf, X.mo, X.rmw are the set of po, rf, mo, and rmw relations, respectively, between events in X.E.

**Derived Relations**. We often use *derived* relations, which are notationally convenient but follow entirely from the primitive relations. Common derived relations are:

• From-read (fr), relating a R with an overwriting W event. For instance, when first reading 1 from X with  $e_5$ : R(X, 1), which is overwritten with 2 by  $e_6$ : W(X, 2), we have an edge fr( $e_5$ ,  $e_6$ ). This relation is derived as fr  $\triangleq$  rf<sup>-1</sup>;mo

*Notation*<sup>5</sup>. rf<sup>-1</sup> is the inverse of rf, *i.e.*, rf<sup>-1</sup>(x, y)  $\triangleq$  rf(y, x); while ';' represents composition of binary relations, *i.e.*, ( $S_1$ ;  $S_2$ )(x, y)  $\triangleq$   $\exists z.S_1(x,z) \land S_2(z,y)$ .

- External relations are those between different threads. For instance, rfe consists of all rf edges between threads; moe is external-mo and fre is external fr. Conversely, internal relations are those within the same thread, such as rfi, moi, and fri. We consider the initialization W events to be internal with events on any thread.

- Same-location relations, such as po<sub>loc</sub>, which relates only po-related (R and W) events that access the same memory location.

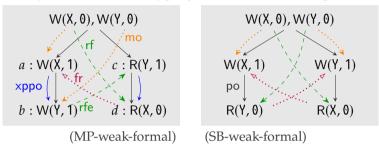

**Examples**. We sometimes draw derived relations. As an example, we redraw the above execution graphs with several such derived relations:

<sup>&</sup>lt;sup>5</sup>We give notations inline but also give an overview in Figure 7 at the end of this chapter.

Observe that the fre edges always follow backwards up an rf edge and then forwards along an mo edge (i.e., fr  $\triangleq$  rf<sup>-1</sup>;mo), thus relating a R to a W overwriting it. For instance, in the left execution we can only read 0 from Y *before* overwriting Y with 1. All fr relations in both executions are external, producing fre arrows, while the mo relations are internal, producing moi arrows.

**Behavior**. When executing a program, only the values in memory are externally observable. In contrast, store buffers and mechanisms to execute instructions out-of-order are internal to a microarchitecture. We thus define the *behavior* of an execution as the final values in all memory locations.

As mo relates all write events to any particular location, per location, the mo-final event captures its final value in memory. An mo-final event is an event which has no mo-successors. Formally, we thus define an execution's behavior as:

```

▶ Definition 2 (Behavior). The behavior of an execution X is: Behavior(X) \triangleq \{\langle e.loc, e.val \rangle \mid e \in X.W \land [\{e\}]; X.mo = \emptyset\}

```

Note that X.W  $\subseteq$  X.E is the set of *write* events in X. The notation [*P*] represents the *identity relation* of set *P*, for any set *P*; meaning  $[P](x, y) \triangleq P(x) \land x \equiv y^6$ .

#### 1.2.2 Program to Execution

An execution (Definition 1) states a particular runtime behavior of a program. When running a program, it often non-deterministically demonstrates one of multiple executions, which differs upon executing it again. The *semantics* of a program is the *set* of all executions the program can show when running on an architecture.

An execution graph does not give the semantics itself, as it does not state whether or not it is observable on an architecture. However, it provides a *language* (Alglave et al., 2014) on which we *can define* semantics. For instance, although we can define an execution for SB-weak, only a semantics—external to that graph—can tell us whether the behavior is possible. In this case, sequential consistency semantics asserts SB-weak is *impossible*, whereas x86 and Arm semantics assert it *is possible*.

While we define semantics over the execution graphs, these graphs connect to the program's syntax. The program generates the execution graph upon execution, while its concurrency primitives (*i.e.*, read, write, and fence instructions) generate the events and relations between them. Within weak memory semantics, we capture *only* the memory events and relations within a program; Other parts of the program's execution, such as arithmetic or thread-local computations, are omitted. The concurrency primitives vary subtly between architectures. However, any primitive can be categorized as a read, write, or fence – or some combination thereof (*e.g.*, RMWs read *and* write). We elaborate on the specific concurrency primitives for various architectures in Section 1.3.

<sup>&</sup>lt;sup>6</sup>We notationally distinguish between propositional equality '≡' and definitional equality '=', which is needed in proof assistants (Chapter 5); we must explicitly prove the former, while the latter holds trivially.

### 1.2.3 Axiomatic Consistency Semantics

With semantics we prescribe which behaviors are observable when executing a program. In particular, we precisely assert which executions are observable on a particular architecture and which are not. We do that with consistency axioms for any particular model. Executions satisfying the axioms are observable, while executions violating it are not. We alternatively call an execution that satisfies all axioms of a model *consistent* with that model. Formally, we denote the *set* of executions of a program  $\mathbb{P}$  consistent with weak memory model M as  $[\![\mathbb{P}]\!]_M$ . Then the *behavior* of  $\mathbb{P}$  under M is the set of behaviors (Definition 2) exhibited by *all* executions in  $[\![\mathbb{P}]\!]_M$ .

**Example: Sequential Consistency**. We illustrate definitions above with the semantics of sequential consistency (Lamport, 1979), where programs must satisfy<sup>7</sup>:

$$(po \cup rf \cup mo \cup fr)$$

is acylic (SC)

This SC axiom states that any execution consistent with sequential consistency *must not* contain cycles consisting of po, rf, mo, and fr edges. As an example, we look at the consistent executions for the Store-Buffering program, which are [Store-Buffering]]<sub>SC</sub>:

Those are *all* executions of Store-Buffering that are consistent with the SC axiom and thus the sequential consistency model. Observe that we presented all po, rf, mo, and fr edges; and that none of those edges together form a cycle, and therefore satisfy SC. The *behavior* of all these executions is  $\{\langle X, 1 \rangle, \langle Y, 1 \rangle\}$ , as 1 is the mo-final value for both X and Y in all executions. Unlike our prior presentations in Section 1.1, the formal behavior does not include the final state of thread-local variable (*i.e.*, a and b).

Of course, weak behaviors are *not* allowed by sequential consistency, of which SB-weak already presented an (informal) example. We now inspect the formal variant of that execution to see whether it actually violates the SC axiom.

<sup>&</sup>lt;sup>7</sup>For presentational simplicity, we ignore RMW instructions here.

Indeed, this execution contains a 'po;fr;po;fr' cycle, which traverses  $a \xrightarrow{po} b \xrightarrow{fr} c \xrightarrow{po} d \xrightarrow{fr} a$ . As it *violates* the SC axiom it is *inconsistent* with the sequential consistency model.

### 1.3 AXIOMATIC WEAK MEMORY ARCHITECTURE SEMANTICS

Although sequential consistency is a simple model, it is *too strong* to describe the behavior of many architectures and languages. As the MP-weak behavior is observable on Arm and the SB-weak behavior is observable on both x86 and Arm, their models need different weak axioms to capture those behaviors. Before going into the specific details of the architecture models, we look at their common axioms.

#### 1.3.1 Common Axioms

Two primary axioms are shared between all models we consider, which are Coherence<sup>8</sup> and Atomicity. We present those common axioms here.

**Coherence.** Coherence states that accesses to the same memory location are sequentially consistent. That is a much weaker requirement than SC from before, as accesses to different locations are *not* sequentially consistent. Formally, we state this axiom as:

$$(po_{loc} \cup rf \cup mo \cup fr)$$

is acylic (Coherence)

Observe that the SB-weak-formal execution contains no violating cycles, as all poedges are between events on different locations. That means the execution is *allowed* by this axiom, which contrasts the stronger SC axiom that had *disallowed* it.

**Atomicity**. Atomicity captures the ordering behavior of RMW instructions that exist on x86, Arm, and RISC-V. An RMW instruction atomically reads and writes from a memory location. That instruction can *fail* when another thread simultaneously writes to the same location, in which case the RMW only generates a R event. However, when it succeeds, it generates both a R and W event, related by an rmw edge. In that case, we know for certain that no other thread had simultaneously written to the same location in memory. The atomicity axiom precisely captures that property:

$$rmw \cap (fre; moe) = \emptyset$$

(Atomicity)

The axiom requires the intersection between rmw and 'fre; moe' to be empty. To illustrate what it disallows, consider a simple program with two threads, where a RMW instruction on the first thread writes 1 while the second threads writes 2:

$$a = RMW(X,1); || X = 2;$$

$$a = RMW(X,1); || X = 2;$$

$$a : R(X,0) \xrightarrow{fre} c : W(X,2)$$

$$b : W(X,1)$$

<sup>&</sup>lt;sup>8</sup>Coherence is sometimes presented differently (*e.g.*, in the Arm model we use in Chapters 4 and 5 (Alglave and Maranget, 2025)), where it is refactored among other axioms. Coherence then still holds, but *implicitly*.

This execution is *disallowed* because it violates the Atomicity axiom. We have edges fre(a, c) and moe(c, b), which means (fre; moe)(a, b). As we also have the edge rmw(a, b), the intersection between those is *not* empty, violating the axiom.

We also show the only two executions for the above program that satisfy Atomicity. In those executions we see no 'fre; moe' paths between the rmw-related events. Intuitively too, the R and W events generated by the RMW instruction are treated *atomically*; no other event observes or interferes with them partially.

1.3.2 x86 Semantics

We now give the weak memory models for various architectures, where we start with the simplest model, which is for x86. Although the ISA is called x86 (Intel Corporation, 2025) its widely-accepted memory model is called x86-TSO (Owens et al., 2009)—TSO stands for *total store order*. The behavior of x86-TSO can operationally be described with local store buffers, whose values other threads cannot observe until they propagate to memory (which we explained in Section 1.1).

An operational semantics (Plotkin, 1981) defines the steps taken by the machine – often an abstract variant of it. For instance, the operational model of x86-TSO (Owens et al., 2009) explicitly captures the machine's internal state with store buffers in every CPU. With that representation, the machine's steps can precisely be described. However, we work with *axiomatic* models, where we do not model those architectural characteristics. Fortunately, the same paper introduces an equivalent axiomatic model, which captures the same behavior, but is more convenient within our context.

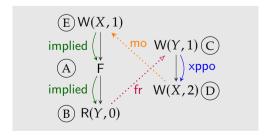

The primary consequence of store buffers is that R–R, R–W, and W–W pairs are ordered along po. In contrast, W–R pairs are not generally ordered, as we have seen above with the SB-weak-formal execution of the Store-Buffering program. The corresponding *x86 global happens before* axiom is as follows:

```

(implied \cup xppo \cup rfe \cup fr \cup mo) is acyclic (XHB)

where xppo \triangleq ((W×W) \cup (R×W) \cup (R×R)) \cap po

implied \triangleq po;[At \cup F] \cup [At \cup F];po

At \triangleq \text{dom(rmw)} \cup \text{codom(rmw)}

```

At a glance, its structure resembles that of SC, where implied and xppo order thread-local events, while rfe, fr, and mo relations capture the order among inter-thread events. Though, fr and mo, also include the thread-local fri and moi edges. The xppo—meaning x86 preserved program order—orders only the R–R, R–W, and W–W pairs

along po, as we expected. In some cases, we may want to order W-R pairs too, for which we can place an intermediate *fence*. The cases of implied describe that thread-local order by stating that anything orders *before* and *after* a fence event F. Finally, implied also orders events produced by RMW operations—CMPXCHG on x86—which are ordered with all preceding and succeeding events, making those operations order like a fence. In the related At definition, the 'dom' and 'codom' functions respectively denote the domain and codomain of the relation they're applied to – rmw in this case. That means, when R(x, y) then  $x \in \text{dom}(R)$  and  $y \in \text{codom}(R)$  for all R, x, and y.

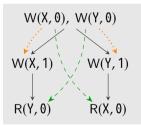

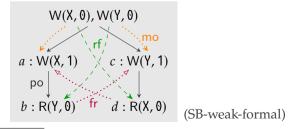

**Example**. To illustrate x86's XHB axiom, we again inspect the weak behaviors of the Message-Passing and Store-Buffering programs – the latter we repeat from above.

In the MP-weak-formal execution, the po edge in the left thread is between W–W events, while it is between R–R events in the right thread. Following the definition of xppo, we obtain those edges between the events in both threads. We thus observe a 'xppo;rfe;xppo;fr' cycle, traversing  $a \xrightarrow{\text{xppo}} b \xrightarrow{\text{rfe}} c \xrightarrow{\text{xppo}} d \xrightarrow{\text{fr}} a$ . Because XHB explicitly disallows that cycle, the weak behavior is *impossible* on x86.

In contrast, the SB-weak-formal execution, the po edges in both threads are between W–R events. Those pairs are explicitly *excluded* from the definition of xppo. Hence, for that execution, there is *no* such cycle. As the XHB axiom disallows cycles –and there is no cycle here– the axiom is *satisfied* meaning the execution is allowed under the x86-TSO model and thus on the x86 architecture.